## SIEMENS

Hand Book 1974

# **SIEMENS**

LSL Low-speed logik Hand Book 1974

### Contents

|                  |         |              |                                                           |    | pag  |

|------------------|---------|--------------|-----------------------------------------------------------|----|------|

| General          | Infor   | mation       |                                                           |    | 6    |

| Summa            | ry of I | ntegrated C  | ircuits available from Siemens                            |    | 8    |

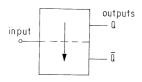

| Logic D          | ata an  | d Symbols    |                                                           |    | 15   |

|                  |         |              |                                                           |    |      |

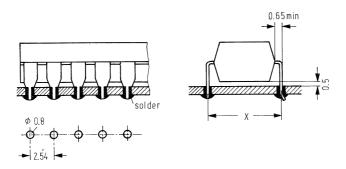

| Mountir          | ng Inst | tructions .  |                                                           |    | 2    |

|                  |         |              |                                                           |    |      |

| Low-S            | peed    | Logic, LSL-  | Series FZ 100                                             |    |      |

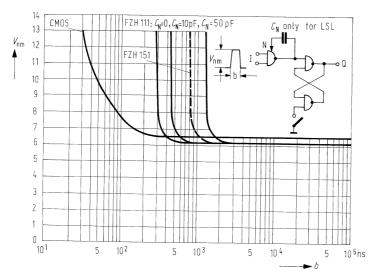

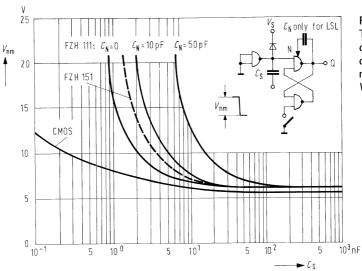

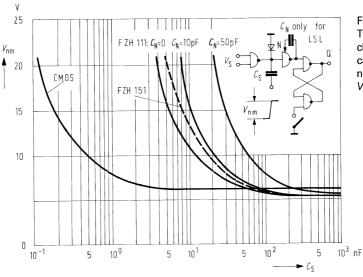

| 1. Nois          | e Imr   | nunity       |                                                           |    | . 2! |

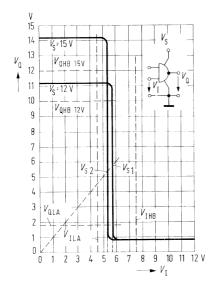

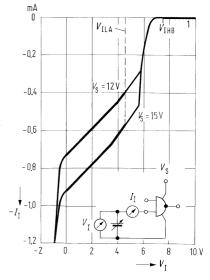

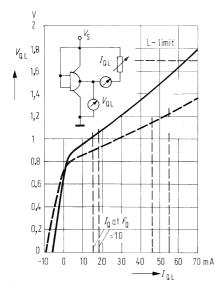

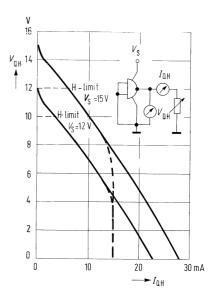

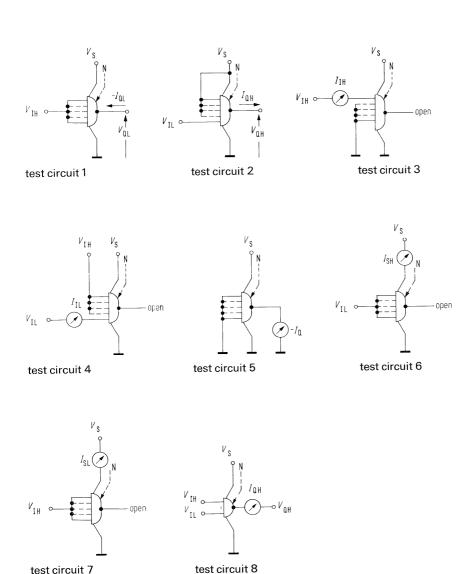

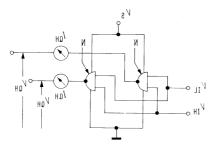

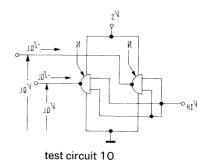

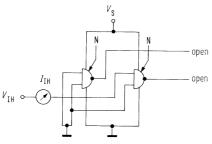

| 2. Stat          | ic Cha  | aracteristic | s                                                         |    | . 29 |

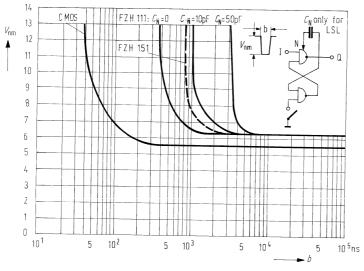

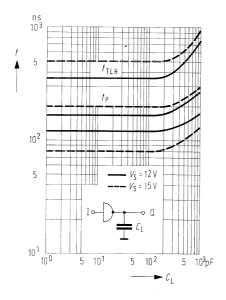

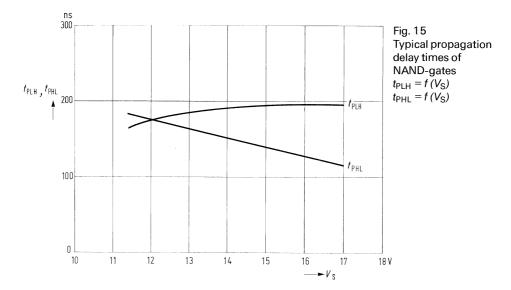

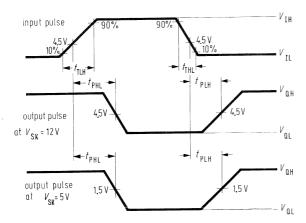

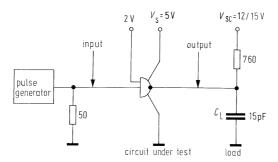

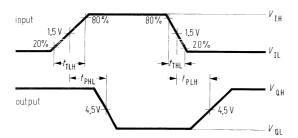

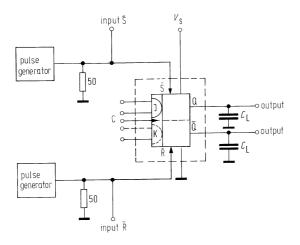

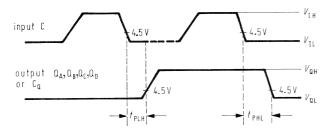

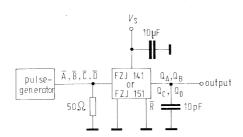

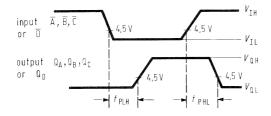

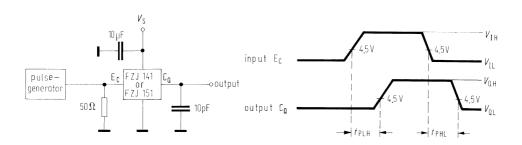

| 3. Dyna          | amic (  | Characteris  | stics                                                     |    |      |

| 4. Elec          | trical  | Characteri   | stics                                                     |    | 4    |

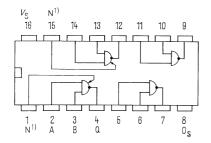

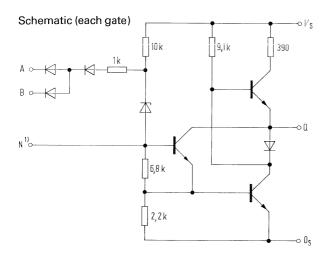

| FZH              | 101,    | FZH 105,     | Quadruple 2-input NAND-gate                               | į. | 44   |

| FZH              | 111,    | FZH 115,     | Quadruple 2-input NAND-gate with N-input                  |    |      |

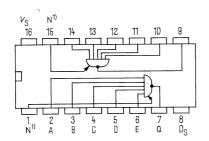

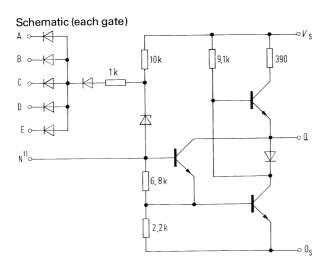

| FZH              | 121,    | FZH 125,     | Dual 5-input NAND-gate                                    |    | 45   |

| FZH              | 131,    | FZH 135,     | Dual 5-input NAND-gate with N-input                       |    | 45   |

| FZH              | 141,    | FZH 145,     | Dual 5-input NAND-powergate with N-input                  |    | 47   |

| FZH              | 151,    | FZH 155,     | Dual AND/OR-gate with N-input                             |    | 48   |

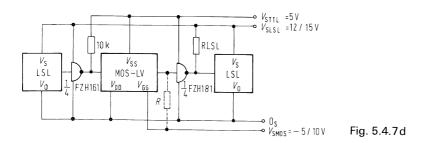

| FZH              | 161,    | FZH 165,     | Quadruple LSL-TTL-level-converter                         |    | 53   |

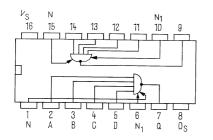

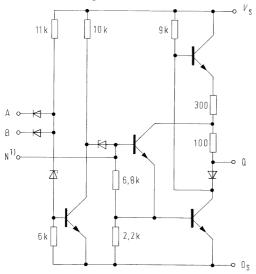

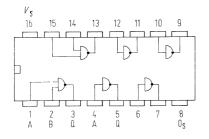

| FZH              | 171,    | FZH 175,     | Dual 4-input NAND-gate with expander nodes N <sub>1</sub> | -  | -    |

|                  |         |              | and N-input                                               |    | 46   |

| FZH <sup>1</sup> | 181,    | FZH 185,     | Quadruple TTL-LSL-level-converter                         |    | 57   |

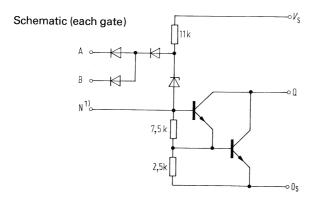

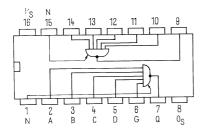

| FZH <sup>1</sup> | 191,    | FZH 195,     | Triple 3-input NAND-gate with N-input                     |    | 59   |

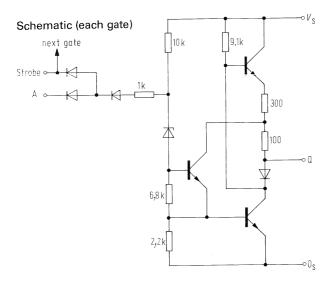

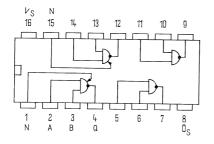

| FZH:             | 201,    | FZH 205,     | Hexinverter with strobe inputs                            |    | 59   |

| FZH 2            | 211,    | FZH 215,     | Quadruple 2-input NAND-gate with open collector output    |    |      |

|                  |         |              | and N-input                                               |    | 63   |

| FZH 2            | 231,    | FZH 235,     | Dual 5-input NAND-gate with open collector output         |    |      |

|                  |         |              | and N-input                                               |    | 63   |

| FZH 2            | 241,    | FZH 245,     | Dual 4-input NAND-Schmitt-Trigger with expander           |    |      |

|                  |         |              | node $N_1$ and $N$ -input                                 |    | 67   |

| FZH 2            | 251,    | FZH 255,     | Quadruple 2-input AND-gate with N-input                   |    | 70   |

| FZH 2            | 261,    | FZH 265,     | Dual 2-input NAND-gate and quadruple Inverter             |    | 70   |

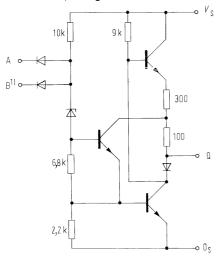

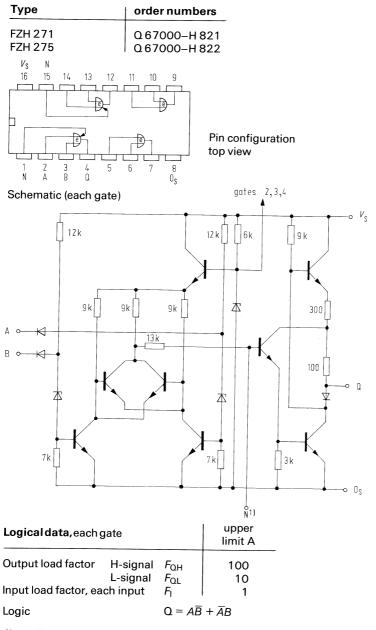

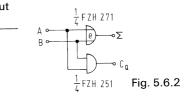

| FZH 2            |         | FZH 275,     | Quadruple 2-input exclusive-OR-gate with N-input          |    | 70   |

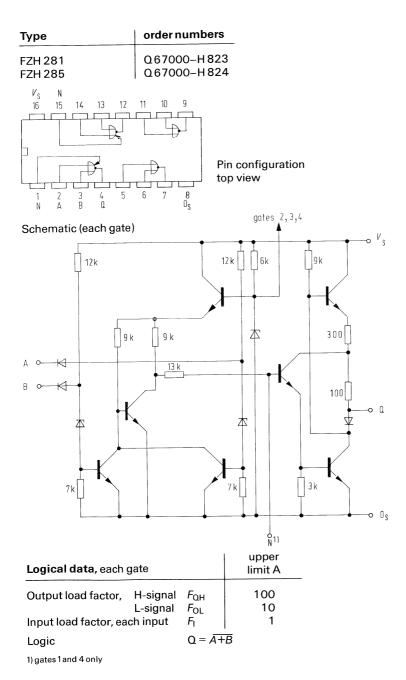

| FZH 2            | 281,    | FZH 285,     | Quadruple 2-input NOR-gate with N-input                   |    | 70   |

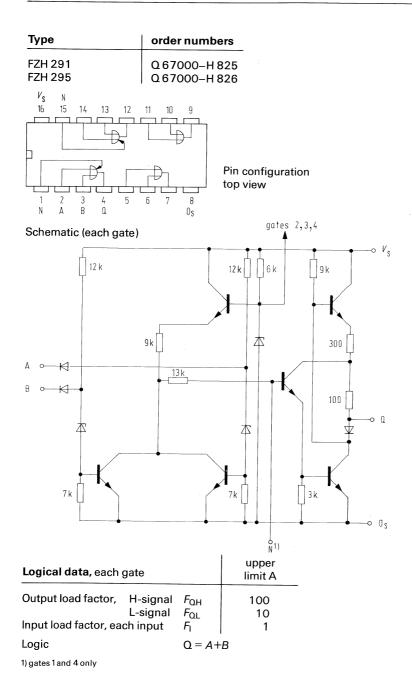

| FZH 2            | 291,    | FZH 295,     | Quadruple 2-input OR-gate with N-input                    |    | 70   |

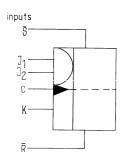

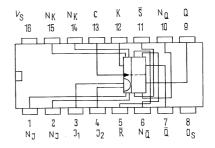

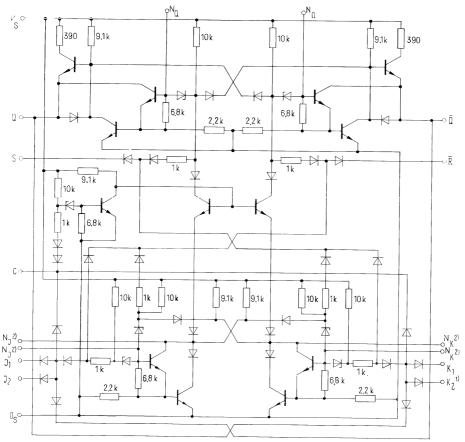

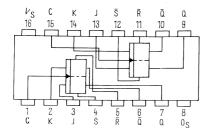

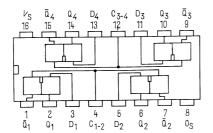

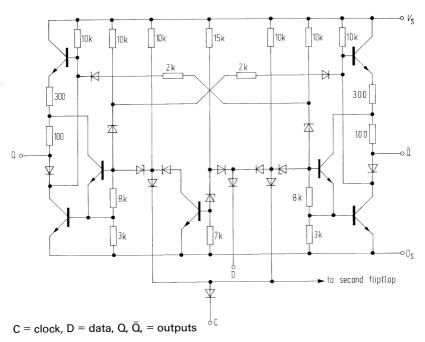

| FZJ ´            | 101,    | FZJ 105,     | JK-master-slave-flipflop with two J and K-inputs          |    | 78   |

| FZJ '            | 111,    | FZJ 115,     | JK-master-slave-flipflop with N-inputs                    |    | 78   |

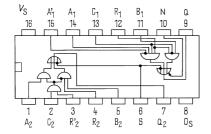

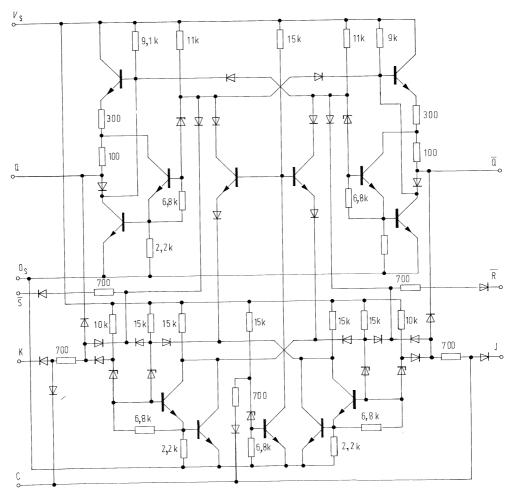

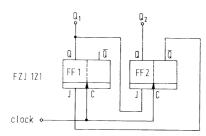

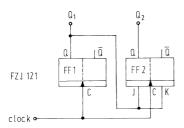

| FZJ ´            | 121,    | FZJ 125,     | Dual JK-master-slave-flipflop with set and reset          |    | 83   |

| FZJ ´            | 131,    | FZJ 135,     | Quadruple D-flipflop                                      |    | 88   |

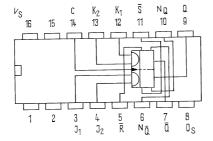

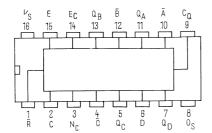

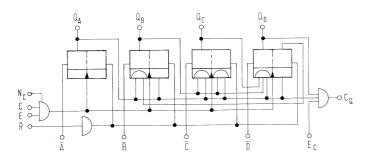

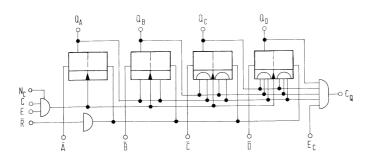

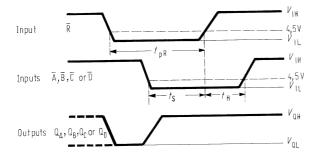

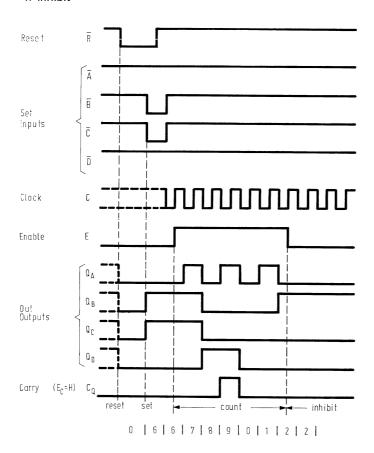

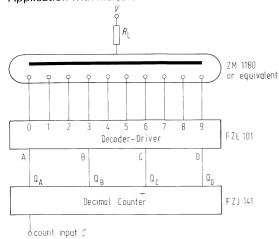

| FZJ ´            |         | FZJ 145,     | Synchronous decimal counter                               |    | 92   |

| FZJ ´            | 141A,   | FZJ 145A,    | Synchronous decimal counter with N-input                  |    | 92   |

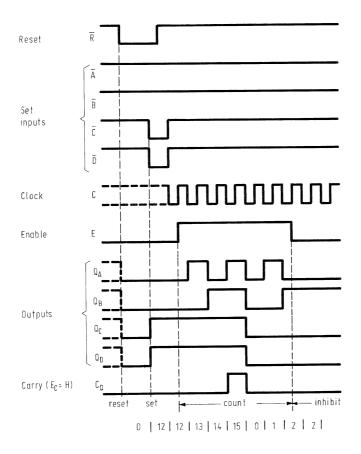

| FZJ 1            |         | FZJ 155,     | Synchronous 4-bit-binary counter                          |    | 92   |

| FZJ 1            | 151A,   | FZJ 155A,    | Synchronous 4-bit-binary counter with N-input             | _  | 92   |

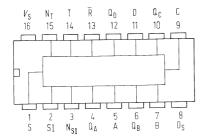

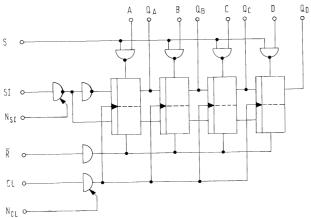

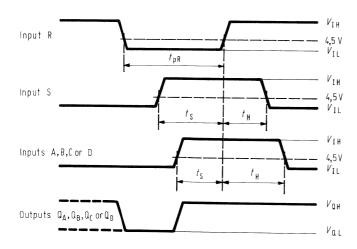

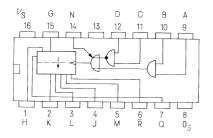

| FZJ 1            |         | FZJ 165,     | 4-bit shiftregister with N-inputs                         |    | 100  |

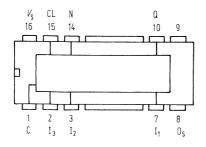

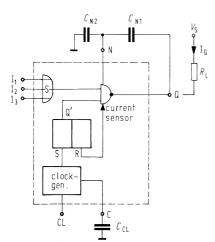

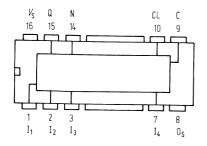

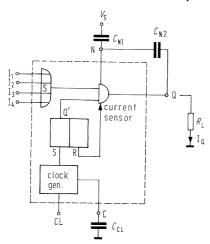

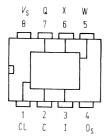

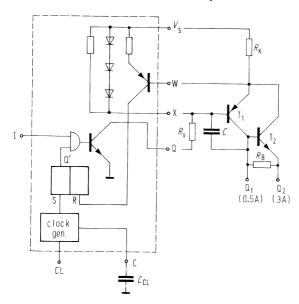

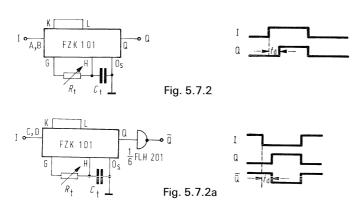

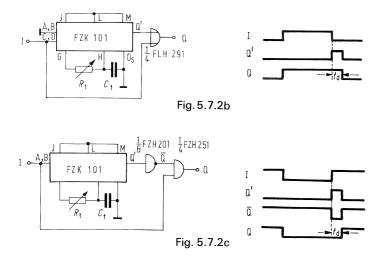

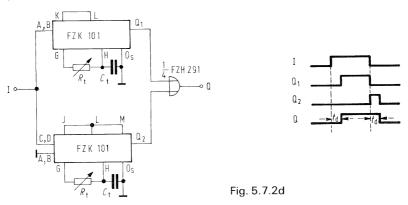

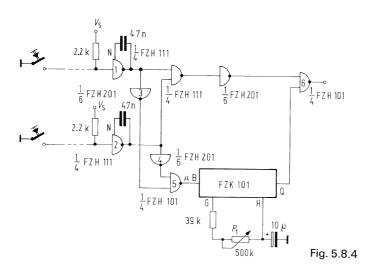

| FZK 1            | 101,    | FZK 105,     | Timing circuit with N-input                               |    | 106  |

|                     | pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | age        |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

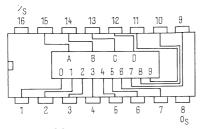

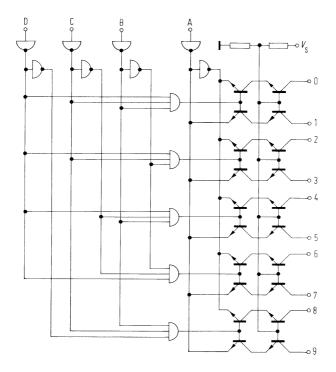

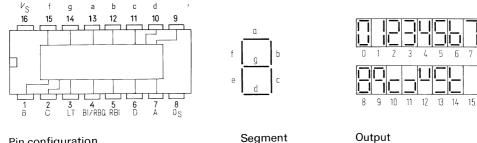

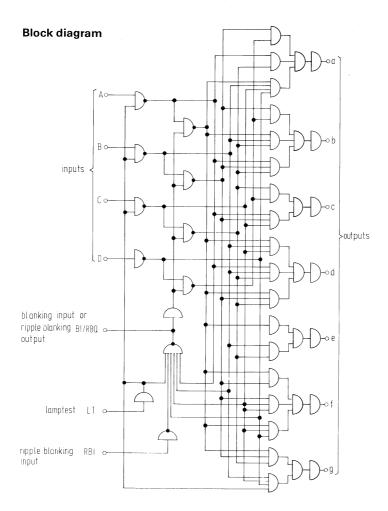

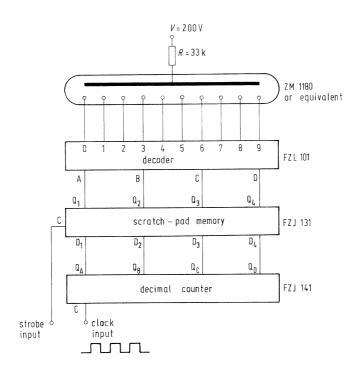

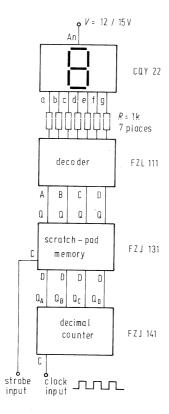

| FZL <sup>*</sup>    | BCD-decimal decoder-driver for indicator tubes 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16         |

| FZL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20         |

| FZL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22         |

| FZL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40         |

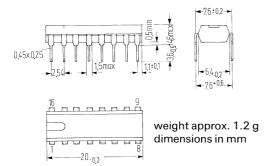

| raok                | ago outimo di arringo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40         |

| 5. App              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43         |

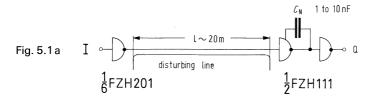

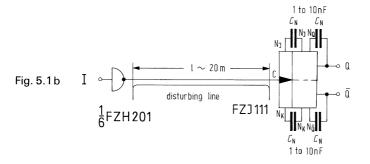

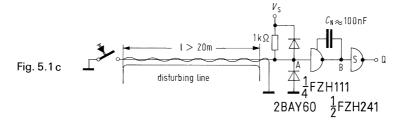

|                     | eystorii concepto comgittate immune zezziemente et inte i z i i z i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51         |

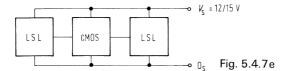

| 5.3                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53         |

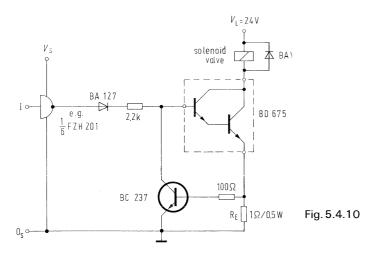

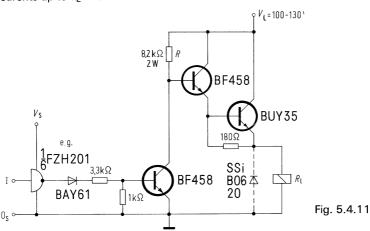

| 5.4                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

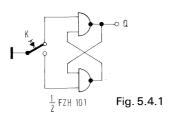

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

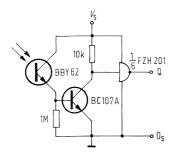

| 5.4.2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

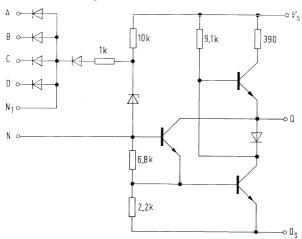

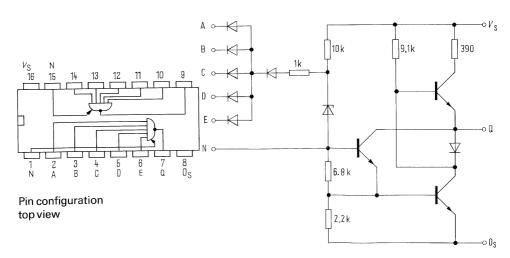

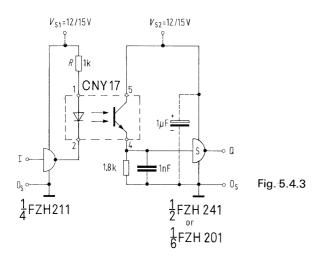

| 5.4.3               | Interfacing with the Optocoupler CNY 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56         |

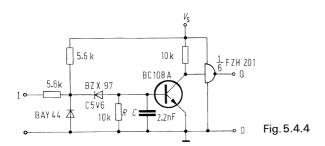

| 5.4.4               | Interface for Negative Input Voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58         |

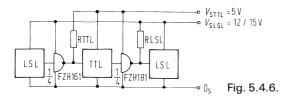

| 5.4.6               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58         |

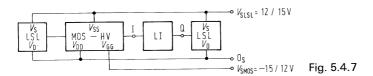

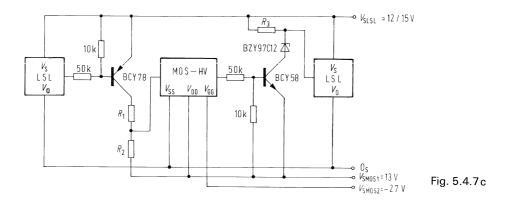

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 59         |

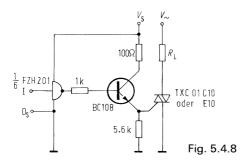

| 5.4.8               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61         |

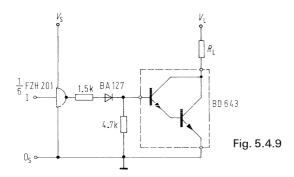

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62         |

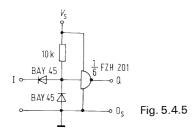

| 5.4.5               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65         |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66         |

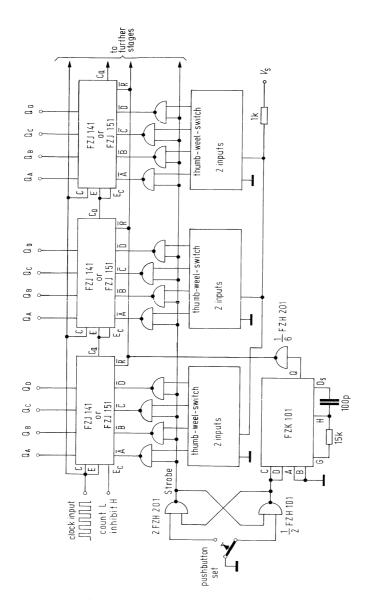

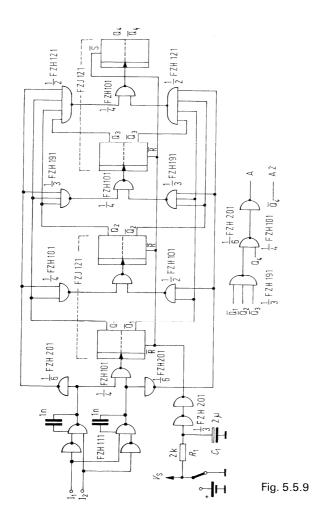

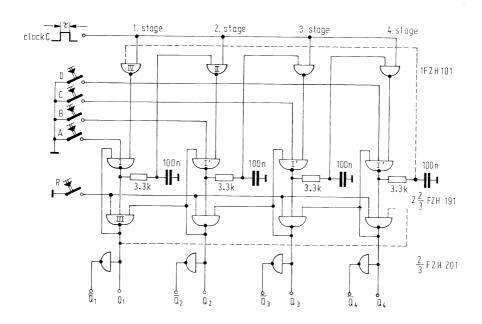

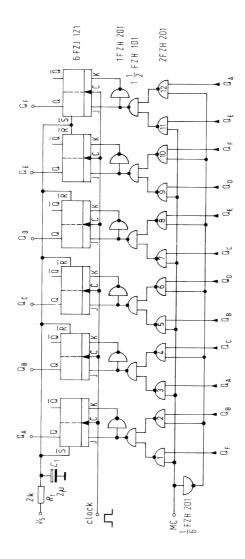

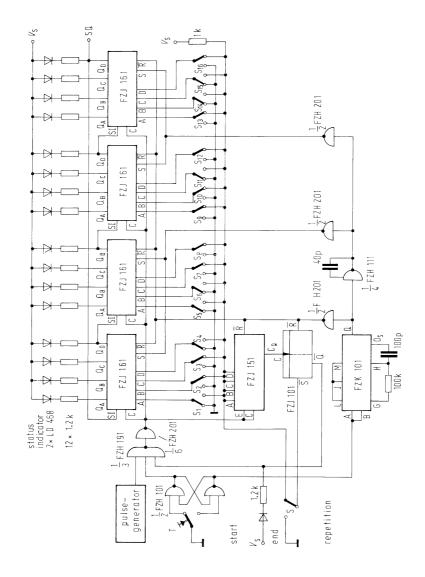

| 5.5                 | Counter and Register Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66         |

| 5.5.1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 5.5.2               | Cyricin circuic countries and a construction of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 167        |

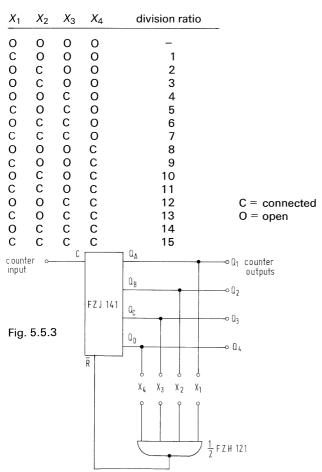

| 5.5.3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 168        |

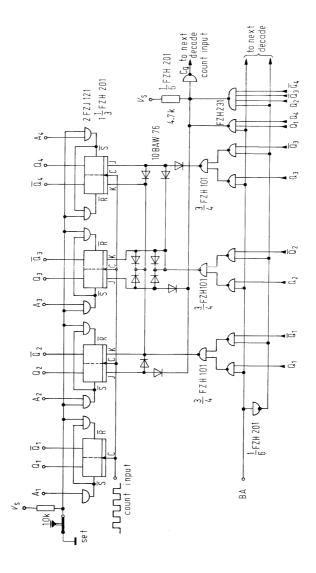

| 5.5.4               | 1.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 169        |

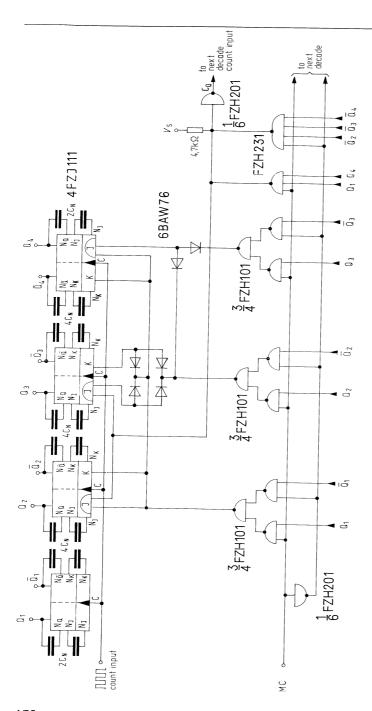

| 5.5.5               | novelene a comman country in the second seco | 71         |

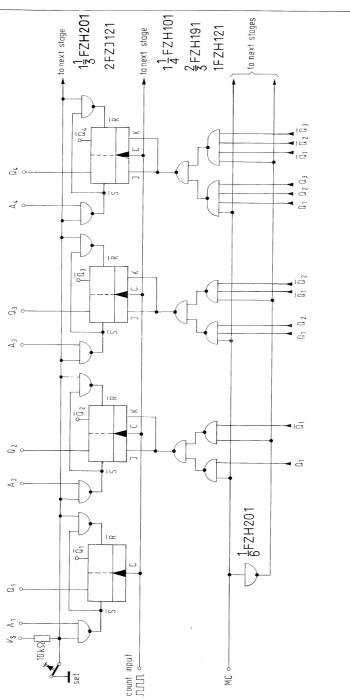

| 5.5.6               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 173        |

| 5.5.7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 175        |